As I write this, funding is at 40% in just the first hour!

In pursuit of my ongoing quest to get Circuit Python working on my ULX3S.... I decided to try out LiteX. I wasn't able to get the rxrbln picorv32 picosoc for ULX3S working (yet) due to some missing files that have not yet been checked in. Part of the journey is simply figuring out which working components to use.

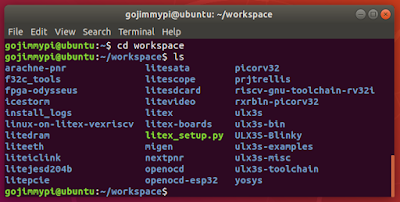

LiteX is included in my full toolchain build for the ULX3S (see my prior blog).

|

| Full ULX3S toolchain directory list |

First: if you are considering getting your own ULX3S from the upcoming Crowd Supply campaign, be aware that only the larger 45F and 85F versions are available options (and capable?) of running the LiteX VexRiscv.

Some key terminology from timvideos to get started: Gateware (as in Field Programmable Gate Array) is the stuff that gets loaded onto the FPGA. Firmware is the application code that the soft CPU will execute. The BIOS is bootstrapping code baked into FPGA.

Note that I installed my development toolchain on WSL Ubuntu. I've also tested the install multiple times on VM's with real Ubuntu. But here, my blog is about using WSL, so all of my stuff is installed on my local C:\workspace directory, or from WSL's perspective: /mnt/c/workpace. On a real Ubuntu machine, simply replace that with your own ~/workspace/ directory.

Why didn't I just put my workspace in the WSL ~/workspace directory instead? Well for one, I can completely wipe out WSL and reinstall, and all my Windows workspace files are still there. I can also access those files easily from Windows and Visual Studio in particular. I'm still waiting on WSL2 (only available to Windows insider / preview at this time, which I chose not to sign up for) - and I believe I need to rip & replace for that version.

LiteX is a code generator. Not only does it create Verilog, but also a bash script to run yosys / nextpnr / ecppack to actually generate an ECP5 FPGA bit file. The fact that it can generate code to build a complete soft CPU is frankly astonishing.

Run the ulx3s.py for the respective device:

There's also an interesting bios.bin file in

Run the ulx3s.py for the respective device:

cd /mnt/c/workspace/litex-boards/litex_boards/targets

# ./ulx3s.py --device LFE5U-45F

./ulx3s.py --device LFE5U-85F

It is not super intuitive where files end up. There's certainly not a lot of documentation for the litex-boards repo

. I searched in powershell:

Get-ChildItem -Recurse | Where-Object { $_.LastWriteTime -ge "03/08/2020 4:00pm" }

the top.bit

file ended up in:

C:\workspace\litex-boards\litex_boards\targets\soc_basesoc_ulx3s\gateware

So from WSL it can be loaded onto the ULX3S like this:

# make sure nothing is using the ULX3S, including VM's, terminal sessions in putty, etc!

cd /mnt/c/workspace/litex-boards/litex_boards/targets/soc_basesoc_ulx3s/gateware

/mnt/c/workspace/ulx3s-examples/bin/ujprog.exe top.bit

Note how Windows executables can be called from the WSL prompt. The same command can be used in a DOS window:

# make sure nothing is using the ULX3S, including VM's, terminal sessions in putty, etc!

c:

cd \workspace\litex-boards\litex_boards\targets\soc_basesoc_ulx3s\gateware

c:\workspace\ulx3s-examples\bin\ujprog.exe top.bit

Stupid things to be aware of: the serial port is running at 11500 8N1. Don't ask me how much time I wasted when using a putty

saved connection for the COM port preset at 19200 and kept wondering why there was no response when trying to connect. I don't think I'll ever make that mistake again. lolThere's also an interesting bios.bin file in

C:\workspace\litex-boards\litex_boards\targets\soc_basesoc_ulx3s\software\bios

My script for synthesizing the CPU ended up in:

/mnt/c/workspace/linux-on-litex-vexriscv/build/ulx3s/gateware/build_top.sh

I had found that build_top.sh file prior to realizing ulx3s.py accepted a device parameter. I have two ULX3S devices, the 12F and the 85F. Guess which one is the defined default for the LiteX build? Yup, the 45F. Did I mention if things are too easy it's no fun? At first I manually edited the build file (note the above call to ulx3s.py does everything, including synthesizing the FPGA VexRiscv core). The default looks like this:

# Autogenerated by LiteX / git: e801dc02

set -e

yosys -l top.rpt top.ys

nextpnr-ecp5 --json top.json --lpf top.lpf --textcfg top.config --45k --package CABGA381 --speed 6 --timing-allow-fail

ecppack top.config --svf top.svf --bit top.bit

Ok, so one of the parameters looks easy enough. Ooph, but what about the "CABGA381"? Well, a quick google search and it turns out that's just a package specification. See the prjtrellis devices.json

for a list of all of them. I'll assume that I each of the ECP5 options on the ULX3S will use the same package, and simply change the "45k" to "85k".There are some bios docs.

Constraint (pin-level) implementation details can be found in platforms/ulx3s.py .

As shown in the ulx3s.py platform file , there's no Ethernet port configured and the serial port is configured for ECP5 pins L4 and M1:

("serial", 0,

Subsignal("tx", Pins("L4"), IOStandard("LVCMOS33")),

Subsignal("rx", Pins("M1"), IOStandard("LVCMOS33"))

),

To build the binaries:

cd $WORKSPACE/litex-boards/litex_boards/targets

./ulx3s.py --device LFE5U-85F --cpu-type picorv32

cd $WORKSPACE/litex-boards/litex_boards/targets/soc_basesoc_ulx3s/gateware

# to program the FPGA as a CPU:

$WORKSPACE/ulx3s-examples/bin/ujprog.exe top.bit

cd /mnt/c/workspace/litex-boards/litex_boards/targets/soc_basesoc_ulx3s/software/bios

litex_term --serial-boot --kernel bios.bin /dev/ttyS15

More to come... see my next blog:

ULX3S RISC-V with LiteX - Part 2

.Copyright (c) gojimmypi all rights reserved. Blogger Image Move Cleaned: 5/3/2021 1:35:54 PM